# **ARCHIVIO DELLA RICERCA**

| University | of Parma   | Research | Repository |

|------------|------------|----------|------------|

| University | oi Paillia | Research | Repository |

| A Low-Power Sigma-Delta Modulator for Healthcare and Medical Diagnostic Applications                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| This is the peer reviewd version of the followng article:                                                                                                                                                                                                                                                          |

| Original A Low-Power Sigma-Delta Modulator for Healthcare and Medical Diagnostic Applications / Boni, Andrea; Giuffredi, Luca; Pietrini, Giorgio; Ronchi, Marco; Caselli, Michele In: IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS. I, REGULAR PAPERS ISSN 1549-8328 (2021), pp. 207-219. [10.1109/TCSI.2021.3112342] |

| Availability: This version is available at: 11381/2898701 since: 2022-01-18T17:05:38Z                                                                                                                                                                                                                              |

| Publisher:                                                                                                                                                                                                                                                                                                         |

| Published DOI:10.1109/TCSI.2021.3112342                                                                                                                                                                                                                                                                            |

| Terms of use:                                                                                                                                                                                                                                                                                                      |

| Anyone can freely access the full text of works made available as "Open Access". Works made available                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                    |

| Publisher copyright                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                    |

note finali coverpage

(Article begins on next page)

# A Low-Power Sigma-Delta Modulator for Healthcare and Medical Diagnostic Applications

Andrea Boni, *Member, IEEE*, Luca Giuffredi, Giorgio Pietrini, Marco Ronchi, and Michele Caselli, *Member, IEEE*

Abstract—This paper presents a switched-capacitor Sigma-Delta modulator designed in 90-nm CMOS technology, operating at 1.2-V supply voltage. The modulator targets healthcare and medical diagnostic applications where the readout of small-bandwidth signals is required. The design of the proposed A/D converter was optimized to achieve the minimum power consumption and area. A remarkable performance improvement is obtained through the integration of a low-noise amplifier with modified Miller compensation and rail-to-rail output stage. The manuscript also presents a set of design equations, from the small-signal analysis of the amplifier, for an easy design of the modulator in different technology nodes. The Sigma-Delta converter achieves a measured 96-dB dynamic range, over a 250-Hz signal bandwidth, with an oversampling ratio of 500. The power consumption is 30  $\mu\rm W$ , with a silicon area of 0.39 mm².

Index Terms—Analog-digital conversion, Sigma-Delta A/D converters, medical diagnostic, healthcare devices, switched-capacitor circuits, low-voltage, low-power, operational amplifiers.

#### I. INTRODUCTION

N the last decade there has been an increasing interest and a growing demand of medical devices for the acquisition and processing of biopotentials, such as electroencephalogram (EEG) and electrocardiogram (ECG) signals. Electronic data acquisition systems can be used also in several other applications for the medical analysis and diagnostic context, such as the Polymerase Chain Reaction (PCR), for the identification and quantifications of viral nucleic acids, micro-organisms, and pathogens [1], [2], the photometry in clinical lab diagnostic [3], and the electrochemistry based on electrochemical cells and an electronic potentiostat for blood analysis [4], [5]. The large part of these applications would greatly benefit from portability of the devices. This requires the minimization of the power consumption of the electronic circuitry to maximize the battery lifetime. Moreover, the same low supply voltage for both analog front-end and digital back-end can be beneficial for these purposes, allowing also a drastic simplification of the power management, with a smaller silicon area [6], [7].

Analog-to-Digital Converters (ADCs) play a fundamental role in the signal acquisition systems. Indeed, they impact significantly the overall Signal-to-Noise ratio (SNR) and power consumption of the acquisition chain. A common characteristic

A. Boni and M. Caselli are with the Department of Engineering and Architecture, University of Parma, Parma, PR, Italy. e-mail: andrea.boni@unipr.it G. Pietrini is with Department of Electrical and Computer Engineering, Mc-Master University, Hamilton, Ontario, Canada. e-mail: pietring@mcmaster.ca L. Giuffredi is with Silis, Parma, PR, Italy. e-mail: luca.giuffredi@silis.it M. Ronchi is with STMicroelectronics, Agrate, Italy. e-mail: marco.ronchi@st.com

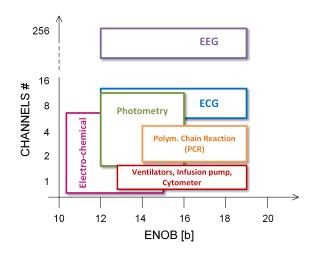

of the above medical and diagnostic devices is the relatively small bandwidth of the signal to be digitized, within a range of few hundreds of Hz. On the other hand, the required effective resolution of the ADC depends on the specific application, which also sets the number of acquisition channels [8]–[12]. Fig. 1 shows the range of the required resolutions and the typical number of channels for the previous-mentioned applications. Additional healthcare devices, where either a gas or a fluid pressure must be sensed and digitized, have been also included. The graph highlights as ADCs with resolutions in the 14-to-16 bits range are suitable for a large number of healthcare and diagnosis applications.

Among state-of-the-art ADCs, Sigma-Delta ( $\Sigma\Delta$ ) converters [13] exhibit the lowest power consumption for the mentioned resolution range and a signal bandwidth of a few hundred hertz [14]. Focusing the analysis on single-loop implementations, switched capacitor (SC)  $\Sigma\Delta$  modulators usually outperform continuous-time implementations. Good performance has been reported for multi-bit SC modulators in the considered application domain [15], but the non-linearity of the Digital-to-Analog Converter (DAC) in the modulator loop requires the implementation of the Dynamic Element Matching (DEM) to transfer the added harmonic distortion into partially shaped noise [16]. However, DEM technique leads to in-band residual tones and to the degradation of the converter SNR [17]. Moreover, the circuit complexity and the area overhead of the DEM control circuits should be taken into account.

An interesting feature of continuous-time (CT) modulators is

Fig. 1. Applications chart of small-bandwidth A/D converters in healthcare and medical diagnostic devices.

1

the built-in low-pass filtering function. This allows the antialiasing filter to be removed with some simplification of the interface circuits. However, they usually exhibits a resistive input impedance, forcing the adoption of an instrumentation amplifier. To overcome this issue and achieve high input impedance, the CT- $\Sigma\Delta$  modulator proposed in [18] adopt a non-inverting integrator. However, the effective resolution (ENOB), at the maximum input gain, is lower than 13 bits and 2.5-V thick-oxide transistors are used, thus calling for an additional technology option. In photometry applications, the low input resistance of the CT modulator is exploited for the current signal source. In [19] a DR larger than 100 dB is achieved combining a front-end 1-st order CT modulator with a single-slope ADC, but a voltage supply of 3.3 V is required and the measured ENOB of the biosensing chain is lower than 11 bits. In [19] a capacitye transimpedance amplifier is merged with a 2-nd order CT modulator, achieving 86-dB DR with a 1.8-V supply.

The paper presents a 1.2-V SC- $\Sigma\Delta$  modulator featuring an effective resolution suitable for a large range of health care and medical diagnostic applications. The front-end integrator is based on a low-noise opamp with a novel implementation of the Miller-Ahuja frequency compensation enabling the near-1-V supply, with the concurrent design optimization for power consumption, voltage gain, and noise [20]. Thanks to the proposed compensation circuit, low sensitivity of the main operational amplifier parameters to both process corner and temperature is achieved in spite of the low supply voltage. A specific feature of the proposed modulator is the capability to operate over a large temperature range with a limited performance degradation. It is worth noticing that state-ofthe-art  $\Sigma\Delta$  ADCs for the considered application domains are seldom characterized over temperature, despite this is mandatory for electronic devices for medical and healthcare markets. Indeed, maintaining the target performance over the temperature range with a low supply voltage, a large signal range, and low power consumption raises significant design issues. Additionally, thanks to low supply sensitivity of the proposed opamp, the modulator achieves the highest power supply rejection (PSR) among the low-voltage ADC in the literature for the considered applications. This performance is of primary importance, taking into account that the converters designed for portable systems are commonly integrated into a mixed-signal chip or a System on a chip (SOC).

The modulator exhibits a conversion energy efficiency that is aligned with state-of-the-art and low-supply ADCs. This was achieved by means of the proposed low-noise opamp and through design optimization, balancing the kT/C and opamp noise to minimize the overall power consumption.

The paper also includes a mathematical model of the opamp for the design optimization based on the target specifications (i.e. gain, bandwidth, slew-rate, phase margin, and noise).

The modulator was implemented in a 90-nm technology to operate over the target temperature range, i.e. from -40°C to 80°C. It exhibits a dynamic range (DR) of 96-dB, 14.8-b ENOB, and more than 70 dB of PSR, with 30  $\mu$ W of power consumption. The experimental results are aligned with the simulations and in agreement with the mathematical model.

TABLE I MODULATOR COEFFICIENTS

| Stage                | Inter-stage coeff. | Feed-forward coeff. | Feed-in coeff. |

|----------------------|--------------------|---------------------|----------------|

| 1 <sup>st</sup> Int. | $c_1 = 0.5$        | $d_1 = 0.2$         | $e_1 = 0.5$    |

| 2 <sup>nd</sup> Int. | $c_2 = 0.0625$     | $d_2 = 0.2$         | -              |

| $3^{rd}$ Int.        | $c_3 = 0.02$       | $d_3 = 0.3$         | -              |

TABLE II

MODULATOR SPECIFICATIONS

| Parameters                | Symbol   | Value | Unit |

|---------------------------|----------|-------|------|

| Sampling frequency        | $f_{CK}$ | 250   | kHz  |

| Signal bandwidth          | $f_b$    | 250   | Hz   |

| Oversampling Ratio        | OSR      | 500   | -    |

| Common-mode input voltage | $V_{cm}$ | 0.5   | V    |

| Full-scale (diff.)        | $V_{FS}$ | 1     | V    |

| Power supply              | $V_{dd}$ | 1.2   | V    |

| Reference - HIGH          | $Vref_P$ | 1     | V    |

| Reference - LOW           | $Vref_N$ | 0     | V    |

| Minimum Dynamic Range     | DR       | 95    | dB   |

The paper is organized as follows. The architecture of the  $\Sigma\Delta$  modulator and the SC integrator is described in Section II. The low-noise opamp used in the front-end integrator is presented in Section III, whereas the complete modulator schematic and other analog blocks is discussed in Section IV. The measurement results are presented and compared with the state-of-the-art  $\Sigma\Delta$  modulators in Section V.

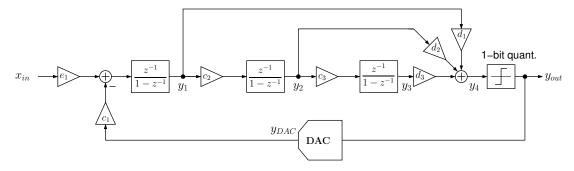

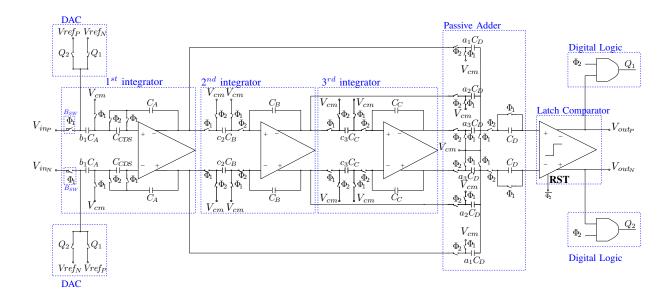

# II. MODULATOR SPECIFICATIONS AND ARCHITECTURE

The block diagram of the proposed 3-rd order  $\Sigma\Delta$  modulator with a single-bit quantizer is shown in Fig. 2. A cascade of integrators with feed-forward (CIFF) topology, was preferred over the implementation with distributed feedback (CIFB) [13], considering the smaller signal swing at the output of each integrator, which makes CIFF modulators preferable with a low supply voltage. Furthermore, this topology exhibits larger inter-stage and feed-in coefficients of the first integrator,  $c_1$  and  $c_1$ , respectively, in Fig. 2, with clear benefits in terms of silicon area and load capacitance. The values of the coefficients obtained with the Delta Sigma Toolbox [21] for the CIFF architecture, and the main specifications of the modulator in Fig. 2 are reported in Table I and in Table II, respectively.

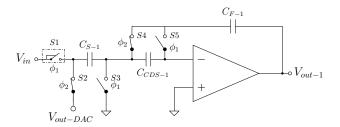

# A. SC Integrator

Each integrator in the modulator of Fig. 2 is based on an opamp with an SC feedback circuit [13]. In low-pass modulators, the low-frequency noise of the opamp may severely affect the effective resolution of the ADC. Thus, a noise cancellation technique such as the correlated-double sampling (CDS) or the chopping modulation (CHM) [22] is mandatory for the first integrator. In the proposed design CDS was preferred to CHM, which pushes the low-frequency noise outside the ADC signal bandwidth, but at the cost of added spurious content in the output spectrum. The single-ended equivalent schematic of the differential integrator is shown in Fig. 3 [23], where

Fig. 2. Block diagram of the third-order  $\Sigma\Delta$  modulator based on the CIFF architecture.

$V_{out-DAC}$  corresponds to the feedback signal  $y_{DAC}$  in Fig. 2. With  $\phi_1 = 1$  and  $\phi_2 = 0$  the input voltage  $V_{in}$  is sampled on  $C_{S-1}$ , while the offset voltage and the low-frequency noise of the opamp are sampled on  $C_{CDS-1}$ . During the integration phase, with  $\phi_1 = 0$  and  $\phi_2 = 1$ , only the difference between  $V_{in}$  and the output of the DAC  $V_{out-DAC}$  is integrated, thus, the offset voltage and the low-frequency noise voltage are removed from the integrator output.

The total harmonic distortion (THD) affecting the output signal of the modulator is caused by two sources of errors: the non-linearity of the input sampling switch, discussed in Section IV, and the settling error at the integrator output, which is mainly ascribed to the opamp limited gain, bandwidth, and slew-rate, together with the stability margin of the integrator in the integration phase [24]. Several behavioural models have been proposed to estimate the Signal-to-Noiseand-Distortion ratio (SNDR) of the modulator from the opamp specifications and the values of the capacitors [24]–[27]. Thus, they provide the design targets for the opamp in the first integrator to achieve the required effective resolution in the mentioned healthcare and diagnostic applications, at the minimum power consumption. The large signal swing at the output of the first integrator, about the 60% of the conversion range of the modulator in Fig. 2, makes challenging the opamp design. Indeed, the estimated lower limits of the voltage gain, bandwidth, and output slew-rate must be fulfilled over the output range of the integrator. For the second and third integrators in Fig. 2, the opamp specifications can be relaxed for power saving, due to the noise suppression factor provided by the modulator loop [13]. For the proposed topology, the noise transfer function (i.e. the inverse of the suppression factor) is -116 dB from the input of the second stage to the modulator input and -162 dB from the input of the third stage

Fig. 3. Single-ended equivalent of the front-end integrator with CDS. With reference to Fig. 2,  $V_{out-1} \equiv y_1$  and  $V_{out-DAC} \equiv y_{DAC}$ .

to the modulator input stage, compared with the -70 dB of the front-end integrator. Therefore, the modulator noise floor in the signal bandwidth is mainly set by the noise of the front-end integrator.

In the integrator circuit with CDS in Fig. 3, the input-referred noise  $v_{n,int}$  is due to noise sources in the sampling  $(\phi_1 = 1)$ and integration ( $\phi_2 = 1$ ) mode:

$$v_{n,int}^2 \approx v_{n,s,sw}^2 + v_{n,i,op}^2 + v_{n,i,sw}^2 + v_{n,cds,op}^2$$

(1)

where  $v_{n,s,sw}^2$  is the contribution of switches  $S_1$  and  $S_3$ in sampling mode,  $v_{n,i,sw}^2$  and  $v_{n,i,op}^2$  are the contributions of switches  $S_2$  and  $S_4$ , and of the opamp, respectively, in integration mode [27], [28]:

$$v_{n,s,sw}^{2} = d \frac{kT}{C_{S-1}}$$

$$v_{n,i,sw}^{2} = d \cdot \alpha_{i,sw} \frac{kT}{C_{S-1}}$$

$$(2)$$

$$v_{n,i,sw}^2 = d \cdot \alpha_{i,sw} \frac{kT}{C_{S-1}}$$

(3)

$$v_{n,i,op}^2 = N_{op} \frac{\omega_t}{4} k_{pk} \tag{4}$$

$$v_{n,cds,op}^2 = \alpha_{cds,op} \cdot v_{n,i,op}^2 \tag{5}$$

where d is either 1 or 2 with respectively a single-ended or a differential integrator, k is the Boltzmann constant, T is the absolute temperature, and  $\alpha_{i,sw}$  depends on the on-resistance of switches  $S_2$  and  $S_4$  and on the opamp bandwidth in the closed-loop configuration. The contribution of the opamp noise in the integration mode is  $v_{n,i,op}^2$  in (4) where  $N_{op}$  is the input-referred noise spectral density of the opamp in the flat region, and  $\omega_t$  is the unity-gain frequency of the integrator loop-gain in integration mode. The coefficient  $k_{pk}$  is added to the basic noise model to take into account the effect of the inband peaking of the input-referred noise spectrum. The input noise of the integrator in Fig. 3 is affected by CDS since the noise of switches and opamp are sampled by  $C_{CDS-1}$ and then transferred to  $C_{S-1}$  [29]. If the contribution of the switches is neglected, only the additional contribution due to the opamp noise must be added, i.e.  $v_{n,cds,op}^2$  in (5), where  $\alpha_{cds,op}$  depends on the  $C_{CDS-1}/C_{S-1}$  ratio. The higher this ratio, the lower  $\alpha_{cds,op}$ . With  $C_{CDS-1} = C_{S-1}$ ,  $\alpha_{cds,op}$  is approximated to unity [27].

The modulator design optimization for the minimum power consumption starts from the noise partitioning of the input noise, between the kT/C component and the opamp in the first integrator, using the equations of  $N_{op}$ ,  $\omega_t$ , and integrator

TABLE III INTEGRATORS' CAPACITORS

| Stage                | $C_{S-\langle i \rangle}$ | $C_{F-\langle i \rangle}$ | $C_{CDS-\langle i \rangle}$ |  |

|----------------------|---------------------------|---------------------------|-----------------------------|--|

| 1 <sup>st</sup> Int. | 2-pF                      | 4-pF                      | 2-pF                        |  |

| 2 <sup>nd</sup> Int. | 128-fF                    | 2-pF                      | -                           |  |

| 3 <sup>rd</sup> Int. | 128-fF                    | 6.4-pF                    | -                           |  |

| Adder                | 250-fF                    | -                         | -                           |  |

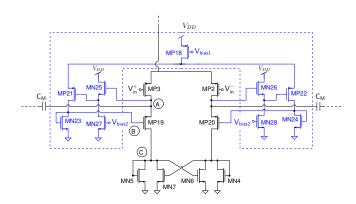

Fig. 4. Schematic of the low-noise opamp in the first integrator (SC-CMFB circuit omitted).

phase margin. It is worth to be noticed that such parameters are usually affected by the opamp non-dominant poles and zeroes if the design is optimized for minimum power. Nevertheless, some modulator models are based on an approximated firstorder transfer function [24], [26], [30], even though this assumption is acceptable only for single-stage opamp's.

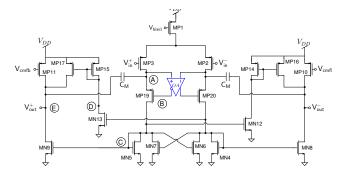

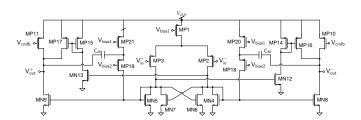

# III. LOW-NOISE OPAMP

With behavioral simulations a minimum DC voltage gain of 50 dB for the opamp was estimated to achieve the target effective resolution. Since the 1.2-V supply makes difficult the exploitation of cascoding techniques in a single gain stage, the two-stage operational amplifier in Fig. 4 was implemented in the integrator. A local positive feedback is introduced in the input stage with MN6 and MN7 boosting the load resistance and thus leading to a higher voltage gain with respect to the amplifier with a simple NMOS-diode load [31]. Improved Miller-Ahuja compensation is implemented to enable concurrent optimization of power consumption, voltage gain and input noise [20]. Indeed, introducing a commongate amplifier, embedded in the first stage (MP19, MP20), in the Miller feedback path allows achieving the same phase margin (PM) with a lower value of transconductance of the second stage  $g_{m9}$  [32], and without any additional power consumption. However, this enhanced Miller compensation adds a pair of complex conjugate non-dominant poles to the opamp transfer function depending on the transconductance of the common-gate stage,  $g_{m19}$  [33]. Since all the transistors are biased in the moderate-to-weak inversion for minimum power consumption,  $g_{m19} \approx g_{m3}$  and, consequently,  $g_{m19}$  cannot be changed without affecting the unity-gain frequency of the opamp, which is proportional to  $g_{m3}$ . If the gate voltage of the common-gate amplifier in the Miller path is controlled through an auxiliary amplifier, OA in Fig. 4, a further degree of freedom is introduced in the design, and the stability margin of the integrator is improved since the value of the complex-conjugate poles frequency and of the dumping ratio is increased [20], [33].

Nevertheless, introducing an auxiliary amplifier with a 1.2-V supply raises relevant design issues due to the cascode configuration of the input stage, considering the process, voltage, and temperature (PVT) variation. Furthermore, the added power consumption should be a small fraction of the opamp consumption, to make the improved Miller-Ahuja compensation suitable for an ultra-low-power design.

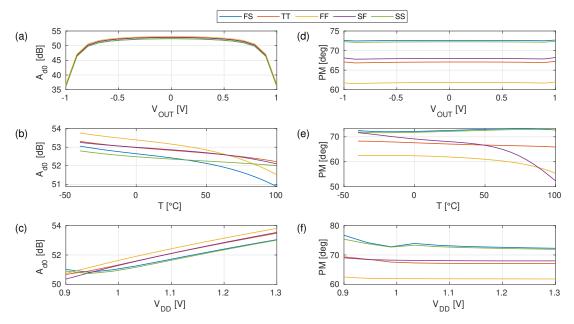

By means of the gain-boosting amplifier in the dashed box of Fig. 5 a low sensitivity is achieved for both the opamp voltage gain and the stability margin of the integrator to the PVT variations, in spite of the near 1-V supply. This fullydifferential auxiliary amplifier is based on input buffers and a PMOS differential pair, with NMOS diodes MN23 and MN24 setting the common-mode output voltage and providing a low output impedance. The DC differential voltage gain  $(A_{aux-0})$ and the angular frequency of the first pole  $(\omega_{aux})$  are:

$$A_{aux-0} \approx \frac{g_{m21}}{g_{m22}} \tag{6}$$

$$A_{aux-0} \approx \frac{g_{m21}}{g_{m23}}$$

$$\omega_{aux} \approx \frac{g_{m23}}{C_{qs23}}$$

$$(6)$$

where  $C_{qs < i>}$  and  $g_{m < i>}$  are the gate-source capacitance and the small-signal transconductance of the *i*-th MOS transistor. The proposed implementation allows satisfying the saturation condition for the involved devices despite the low supply voltage. Indeed, MP19 is always in the saturation region if

$$V_B \ge V_C + V_{Tp} \tag{8}$$

where  $V_B$  and  $V_C$  are the voltages at nodes B and C in Fig. 5, and  $V_{Tp}$  is the threshold voltage of PMOS devices. Since  $V_B \approx V_C \approx V_{Tn}$ ,  $V_{Tn}$  being the threshold voltage of NMOS devices, the condition in (8) is always satisfied over the process and temperature corner space, since  $V_{Tp} < 0$ . The saturation condition for the opamp input devices is

$$V_{in}^+, V_{in}^- \ge V_A + V_{Tp} \approx V_{Tn} \tag{9}$$

where  $V_{gs23} \approx V_{Tn}$  and  $V_{sg19} \approx -V_{Tp}$  have been assumed. Therefore, a suitable range for the common-mode input voltage is obtained over the PVT variations at 1.2-V supply. Since the implemented compensation allows to scale down the

Fig. 5. Schematic of the auxiliary amplifier (blue lines in the dashed box) for the transconductance enhancement of MP19 and MP20.

Fig. 6. From (a) to (c) and from (d) to (f): simulated opamp DC gain and phase margin (with unity feedback factor) over corners and vs. the DC output voltage, temperature, and supply voltage.

transconductance of the output devices  $(g_{m9})$ , the bias current of the output stage is reduced accordingly for power saving. Therefore, a dynamic bias (class-AB) is introduced to maintain a suitable slew-rate with a low quiescent current and, thus, to limit the settling error of the integrator [26].

The simulated DC-gain and phase margin (with unity feedback factor) over the corner space and vs. the integrator DC output voltage, temperature, and supply are shown in Fig. 6(a)-to-(f). The results confirm the expected low sensitivity of the critical opamp specs, allowing to achieve the target modulator performance over the full PVT space.

#### A. Small-signal and noise analysis

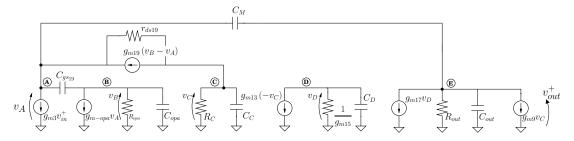

Assuming the 3-dB bandwidth of the auxiliary amplifier large enough not to affect the transfer function of the opamp, the small-signal equivalent circuit of the left-side of the amplifier in Fig. 4 can be simplified as in Fig. 7. The expression of each equivalent resistance and capacitance are reported in Appendix with a detailed circuit analysis. A fifth-order transfer function is obtained for the voltage gain:

$$A_d(s) \equiv \frac{v_{out}^+}{v_{in}^+} = \frac{A_{d-0} \cdot \left(a_4 s^4 + a_3 s^3 + a_2 s^2 + a_1 s + 1\right)}{b_5 s^5 + b_4 s^4 + b_3 s^3 + b_2 s^2 + b_1 s + 1}$$

(10)

The equation of the DC-gain is:

$$A_{d-0} = R_C R_{out} g_{m3} g_{m9} \cdot \left( 1 + \frac{g_{m13} g_{m17}}{g_{m9} g_{m15}} \right)$$

(11)

If  $C_C$  and  $g_{m9}$  are, respectively, lower and higher than critical values  $C_{C-crit}$  and  $g_{m9-crit}$ , the second pole of  $A_d(s)$  is real, while the third and fourth poles are complex conjugates. The case corresponding to  $C_C \ge C_{C-crit}$  or  $g_{m9} < g_{m9-crit}$  is not relevant because it corresponds to a small phase margin.

Approximated analytic expressions of the first, second, and third pole  $(p_1, p_2, \text{ and } p_3)$  are reported in Appendix. The frequency  $z_1$  of the dominant zero is obtained from  $a_1$ :

$$z_1 \approx -\frac{1}{a_1} \approx -\frac{g_{m9} g_{m15} + g_{m13} g_{m17}}{g_{m9} C_D}$$

(12)

Thus, considering the analytic expression of the second-pole frequency  $p_2$  in (28), a pole-zero cancellation is obtained, if the following conditions hold:

$$g_{m9} R_C >> \frac{C_{out}}{C_M}$$

$$g_{m9} R_C >> 1$$

$$(13)$$

$$q_{m9} R_C >> 1 \tag{14}$$

This is achieved with the local feedback boosting the equivalent load resistance of the first stage  $(R_C)$ . The pole-zero cancellation is a relevant benefit of this opamp architecture, leading to improved bandwidth and stability margin.

Since the second zero in the transfer function lies in the right-half plane (RHP), it should be taken into account in the stability-margin estimation. Finally, if the contributions of the high-frequency zeroes  $(z_3, z_4)$  and of the fourth pole  $p_4$  are neglected, an approximated expression for the phase margin of the integrator in Fig. 3 is obtained:

$$PM = 90^{\circ} - atan\left(\frac{2\delta_3 \cdot (\omega_t/|p_3|)}{1 - (\omega_t/|p_3|)^2}\right) - atan\left(\frac{\omega_t}{z_2}\right) \quad (15)$$

where  $|p_3|$  and  $\delta_3$  are the complex frequency and the dumping factor of the third-pole,  $z_2$  is the frequency of the RHP zero, and  $\omega_t$  is the unity gain frequency of the integrator loop gain. Therefore, the DC gain of the auxiliary amplifier is sized from (15) to achieve the target stability margin.

The spectral power density of the input-referred voltage-noise

Fig. 7. Small-signal equivalent circuit of left side of the amplifier in Fig. 4.

$(v_{n,in}^2)$  of the opamp in Fig. 4 is obtained from its small-signal equivalent circuit, and depends only on the input stage:

$$v_{n,in}^2 \approx \frac{8 k T \gamma_p}{g_{m3}} \cdot \left[ 1 + \frac{(g_{m_5} + g_{m_7}) \gamma_n}{g_{m3} \gamma_p} \right]$$

(16)

where  $\gamma_n$  and  $\gamma_p$  are the gamma factors of the thermal channel noise of NMOS and PMOS devices. The flicker noise sources are not considered since their effect is removed with the CDS at the integrator-level. The contribution of the auxiliary amplifier is negligible in the integrator bandwidth, since the source nodes of MP19 and MP20 are connected to ground through a high equivalent impedance. A similar equation can be obtained for a 2-stages Miller-compensated opamp with a high-gain input stage [34]. Therefore, the implemented opamp achieves significant improvements in terms of bandwidth (due to pole-zero cancellation), stability margin, and power saving, without any degradation of the noise performance with respect to the basic Miller opamp.

## B. Power-driven opamp design

In this section we provide an accurate model to link the opamp noise and bandwidth to the power consumption. Since the amplifier is optimized for minimum power consumption, all the devices are biased in moderate-to-weak inversion region.

The bias current of the first stage  $(I_{d1})$  is sized on the basis

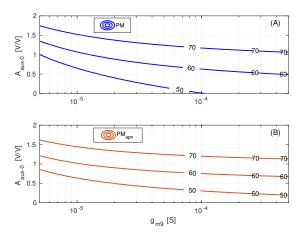

Fig. 8. Contour plot of  $PM(A_{aux-0}, g_{m9})$  at  $50^{\circ}$ ,  $60^{\circ}$ , and  $70^{\circ}$  levels. A: exact PM value from  $A_d(j\omega)$ ; B approximated PM with equation in (15).

of the value of  $Max\left[v_{n,in}^2\right]$ . From (16) with  $\gamma_p \approx \gamma_n$ , the following equation is obtained:

$$I_{d1} \ge \frac{n v_{th}}{\alpha_n} \cdot \frac{8 k T \gamma_p}{Max \left[v_{n,in}^2\right]}$$

(17)

where  $\alpha_n$  is the relative contribution of the input devices M2 and M3 to the power spectral density of the input-referred noise voltage. The Miller capacitance,  $C_M$  is sized from (50). If the slew-rate resulting from this sizing is not compatible with the maximum acceptable settling error, the current in first stage must be increased. In order to limit the noise contributions of the load devices well below  $(1-\alpha_n)\cdot Max\left[v_{n,in}^2\right]$ , they are sized for a higher Inversion Factor (IF) than the input transistors [35]. The following condition must be guaranteed over the PVT space to make the stability margin independent of the auxiliary amplifier:

$$\omega_{aux} \ge 10 \cdot \omega_t \tag{18}$$

From (7) and approximating the gate-source capacitance with the worst-case value corresponding to the gate-to-channel capacitance, a lower bound for the IF of MN23 and MN24 is found:

$$\omega_{aux} \ge \frac{IF_{23}}{0.5 + \sqrt{0.25 + IF_{23}}} \cdot \frac{3k'_n v_{th}}{L_{23}^2 C_{ox}} \ge 10 \,\omega_t$$

(19)

The minimum bias current of MN25 and MN26 is obtained by setting the pole introduced by the input buffer stage at least one decade over the unity loop-gain frequency  $\omega_t$ .

The equivalent capacitance  $C_D$ , introduced by MN13, MN15, and MN17 used for the dynamic control of the output current, affects the frequency of the second pole and first zero as in (28) and (12). The step response of the amplifier is improved if the pole-zero  $(p_2$ - $z_1)$  cancellation occurs at a frequency higher than  $\omega_t$ . From (34) and (12), and assuming  $g_{m9}$   $R_C$  much larger than  $C_{out}/C_M$ :

$$z_1 \approx p_2 \approx \frac{g_{m17}}{C_{qs17}} \cdot \frac{g_{m9} + g_{m13}}{g_{m9}} \ge \omega_t$$

(20)

Therefore

$$\frac{g_{m17}}{C_{gs17}} \ge \omega_t \cdot \frac{g_{m9}}{g_{m9} + k_{AB1} g_{m5}} \tag{21}$$

where  $k_{AB1} \equiv (W/L)_{13}/(W/L)_{5}$  is the current gain of the MN4-MN13 mirror. A lower bound for  $g_{m17}/C_{gs17}$  is obtained from (21), leading to a lower limit for  $IF_{17}$  (and  $IF_{15}$ ). Furthermore, the lower  $k_{AB1}$ , the lower the power consumption of the control circuit at the cost of a higher  $g_{m17}/C_{gs17}$ . The condition in (21) can be fulfilled by reducing

TABLE IV

SPECIFICATIONS OF THE LOW-NOISE OPAMP

| Metric                    | Value | Unit           |

|---------------------------|-------|----------------|

| $A_{d-0}$                 | 53    | dB             |

| $\omega_t$ @ $H_r$ =1     | 14.1  | Mrad/s         |

| SR                        | 1.4   | V/μs           |

| Noise                     | 38    | nV <i>l√Hz</i> |

| Load Capacitance $(C'_L)$ | 2.33  | pF             |

| Power consumption         | 15    | $\mu W$        |

the length  $L_{17}$  of MP17 (and MP15), leading to a lower DC voltage gain, or by increasing the IF of M17, with a detrimental effect on the output voltage swing. The current gain of the mirror MP17-MP15  $k_{AB1}$  must be sized to achieve a maximum drain current of M17 compatible with the target slew-rate (SR) limit:

$$\frac{I_{d1} k_{AB1} k_{AB2}}{C_L'} \ge SR \tag{22}$$

The DC voltage gain of the auxiliary amplifier  $A_{aux-0}$ , and the transconductance of the output stage  $g_{m9}$  are sized on the target phase margin (PM). To this aim the value of PM at different values of  $A_{aux-0}$  and  $g_{m9}$  was calculated from the transfer function  $A_d(j\omega)$  in (10) and resorting to the approximation in (15). The contour plots of PM are shown in Fig. 8, where the other small-signal parameters of the circuit have been sized for the target resolution, at the minimum power consumption. The results show that a value of  $A_{aux-0}$ in the range of 1-to-2 is enough for a large stability margin and power saving in the output stage. It should be noticed that the approximation in (15) is in a good agreement with the exact value of PM (from the full transfer function) for values higher or equal to 60°. Therefore, with our circuit model, it is possible to easily size  $A_{aux-0}$  and  $g_{m9}$  for the minimum power consumption at the target PM. From (6) and the gmover-Id dependence on IF [35],  $A_{aux-0}$  is written as:

$$A_{aux-0} = -\frac{n_p}{n_n} \cdot \frac{0.5 + \sqrt{0.25 + IF_{23}}}{0.5 + \sqrt{0.25 + IF_{21}}}$$

(23)

The bias current of MN9 is sized from the target value of  $g_{m9}$ :

$$I_{d9} \ge n \, v_{th} \, g_{m9} \cdot \left(0.5 + \sqrt{0.25 + IF_9}\right)$$

(24)

where  $IF_9 = IF_5$ . The value of  $I_{d9}$  must be compatible with the minimum slew-rate limit of the opamp. Since the drain

TABLE V

DEVICE SIZE AND BIAS

| device       | W/L    | $g_m/I_d$ |

|--------------|--------|-----------|

| MP3          | 9/0.9  | 20.9      |

| <i>M</i> P19 | 9/0.45 | 23.0      |

| MN5          | 2.4/3  | 14.4      |

| MN7          | 1.2/3  | 13.3      |

| MN9          | 4.8/3  | 14.3      |

current of MN9 is set by the MN5-MN9 mirror, the transient peak value corresponds to twice the DC value:

$$I_{d9} \ge 0.5 \, C_L' \, SR \tag{25}$$

The simulated specifications (typical corner) of the low-noise opamp are reported in Table IV. The size and bias (i.e.  $g_m/I_d$ ) of main devices are listed in Table V.

#### IV. MODULATOR: CIRCUIT AND BUILDING BLOCKS

The complete modulator circuit is shown in Fig. 9, where  $C_A$ =4.1 pF,  $C_B$ =2 pF, and  $C_C$ =6.1 pF. In the second and third integrator the specifications for the amplifier can be relaxed. Therefore, the common-gate stage in the Miller feedback path is moved outside from the input stage, and no auxiliary amplifier is used. The schematic is shown in Fig. 10. This amplifier exhibits lower power consumption compared to the opamp in the front-end integrator in Fig. 4, at the cost of higher noise and worst dynamic performance. However, the noise suppression factor of the 2-nd and 3-rd integrator makes this opamp fully compatible with the target resolution of the modulator.

The signal-sampling switch in the first integrator may have a relevant impact on the overall harmonic distortion of the modulator. Considering that the swing of the input signal is about 80% of the supply voltage, a CMOS transmission gate cannot be used in the front-end. Hence, bootstrapped switches with thin-oxide transistors are included in this design [36]. The switch exhibits a simulated THD lower than -100-dB over the PVT variations, with back-annotated layout parasitics, up to the maximum signal amplitude.

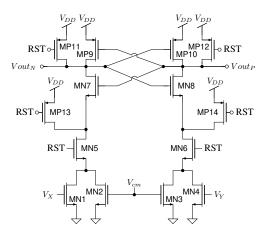

The single-bit quantizer is implemented with a dynamic latch comparator, shown in Fig. 11. With RST at low level, the latch is in reset mode with the outputs,  $Vout_P$  and  $Vout_N$ , at the supply voltage  $(V_{DD})$ . When RST goes high, the latch is in regeneration/hold mode.

# V. MEASUREMENT RESULTS

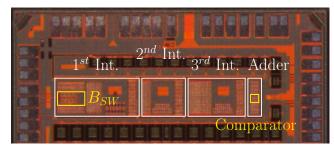

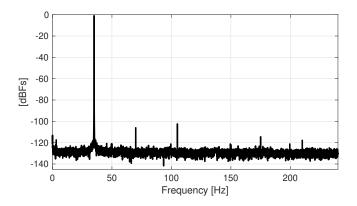

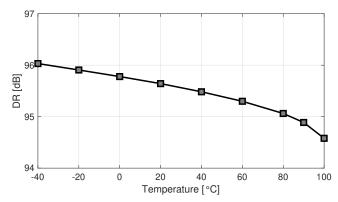

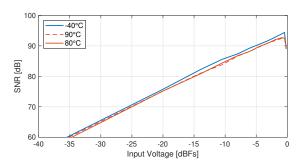

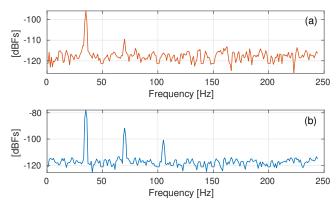

The proposed third-order modulator was implemented in STM 90-nm digital CMOS technology, with the Metal-Insulator-Metal (MIM) capacitor as the only technology option. The chip photograph is shown in Fig. 12, where the bootstrapped switch  $(B_{SW})$ , the integrators, and the quantizer are highlighted. The silicon area is 0.39-mm<sup>2</sup>, including the clock tree. The silicon samples are packaged in a Quad Flat Package (QFP) with an exposed back pad, internally connected to the chip ground by multiple down-bonds. Fig. 13 shows the FFT spectrum of the output bitstream with an input sinewave of 35-Hz frequency and amplitude of -0.91 dBFs, i.e. normalized to the modulator full-scale. The second harmonic at -105 dBFs is due to a layout imperfection, causing a mismatch between the positive and the negative signal path. After a layout fix, this harmonic is pushed below -120 dBFs as shown by post-layout simulations with back annotated parasitics. In the same output spectrum starting from 30 mHz, the 1/f noise contribution is negligible, as a result of the lowfrequency noise cancellation in the first integrator. The plot in Fig. 14 shows the modulator SNR and SNDR versus the

Fig. 9. Full schematic of the  $\Sigma\Delta$  modulator.

normalized input signal amplitude, with a peak-SNR of 93 dB. The proposed converter was measured over the target temperature range with an ACS climatic chamber, featuring a temperature stability within  $\pm 0.5$  °C. From the measured dynamic range (DR) vs. the temperature in the plot of Fig 15, a sensitivity of -8.4 mdB/°C is estimated over the -40°C to +80°C range. This performance slightly degrades for temperatures above the considered range. In Fig. 16 the modulator SNR at the extreme temperatures is plotted vs. the input signal amplitude. The performance achieved at 90°C confirms the smooth degradation of the noise performance beyond the maximum specified temperature. The supply rejection of the modulator was measured with a 35-Hz, 100-mV sine-wave signal superimposed to the 1.2-V supply. As shown in the output spectrum in Fig. 17(a), a 76-dB PSR was achieved. The output spectrum in Fig. 17(b) was obtained with a common-mode input signal of 100-mV amplitude and with the modulator inputs shorted. The fundamental tone at -77 dBFs corresponds to a common-mode rejection (CMR) of 57 dB. A summary of the measured performance is reported in Table VI. The proposed design was compared to the state-of-the-art SC and CT modulators suitable for the healthcare and medical diagnostic applications in the chart of Fig. 1. To this aim, low-pass modulators with input bandwidth within 1 kHz and effective resolution higher than 10 bits was considered [52]. The Schreier Figure of Merit (FOM) was used for this

Fig. 10. Schematic of the class AB opamp for the 2nd and 3rd integrator.

Fig. 11. Schematic of the latch comparator.

comparison [13]:

$$FOM \equiv DR + 10 \cdot log_{10} \left(\frac{BW}{Pw}\right) [dB]$$

(26)

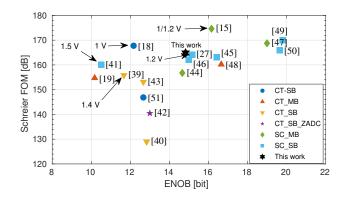

where BW and Pw are the input bandwidth (in Hz) and the power consumption (in W) of the modulator. The result of the comparison is shown in Fig. 18, where SC\_SB and

Fig. 12. Chip photograph, with main modulator blocks in white boxes. Bootstrapped switches of the first integrator, and comparator in yellow boxes.

Fig. 13. Measured output spectrum with a 35-Hz sinusoidal input. The measured frequency is limited to the input bandwidth.

| MEASURED PERFORMAN   |        |

|----------------------|--------|

| Input bandwidth (BW) | 250-Hz |

| G 1 1                | 1.0.37 |

TADLE M

| Input bandwidth $(BW)$ | 250-Hz      |

|------------------------|-------------|

| Supply voltage         | 1.2-V       |

| Power consumption      | 30-μW       |

| Peak SNR               | 93-dB       |

| Peak SNDR              | 91-dB       |

| Peak SFDR              | 100.5-dB    |

| DR                     | 95.6-dB     |

| DR sensitivity         | -8.4 mdB/°C |

| THD                    | -101-dB     |

| PSR                    | 76-dB       |

| TEMP                   | [-40°,+80°] |

|                        |             |

SC\_MB correspond to switched-capacitor modulator with single-bit and multi-bit quantizer, respectively, CT\_SB and CT\_MB to continuous-time single-bit and multi-bit modulators, and CT\_SB\_ZADC to CT modulators with zoom-adc [42]. Among the modulators with a resolution higher than 12.5 b and a supply voltage lower than 1.8 V, the proposed modulator exhibits one of the highest FOM and it is overcome only by the multi-bit SC design in [15], which, however, requires a pair of supply voltages (i.e. 1 and 1.2 V), with increased complexity and area for the power management circuits. Compared with our previous 3-rd order CIFF architecture in [27], where the opamp in the first integrator is compensated with the basic Miller configuration, the proposed implementation, integrating a low-voltage Miller-Ahuja

Fig. 14. Measured SNR and SNDR vs. input amplitude.

Fig. 15. Measured DR over the -40°C-to-100°C temperature range.

Fig. 16. Measured SNR vs. input amplitude at -40°C, 80°C, and 90°C.

compensation, achieves lower power consumption and hence higher FOM. The significant FOM result was achieved thanks to the low-noise opamp in the first integrator and the global design optimization for the minimum power consumption. The details of some silicon-proven modulators considered for the comparison are reported in Table VII. It should be noticed that the proposed design exhibits the highest PSR among the modulators with a sub-1.8-V supply. Restricting the survey to the low-voltage modulators with more than 12-b resolution, only the design reported in [15] outperforms our implementation in terms of current consumption, but with a larger silicon area and at the cost of two distinct supply voltages. It is worth noticing that the proposed modulator was

Fig. 17. Measured output spectrum with: (a) a 35-Hz, -20-dBFs signal superimposed to the supply, (b) a 35-Hz, -20-dBFs common mode input signal. Modulator inputs are shorted in both cases.

| TABLE VII                  |             |

|----------------------------|-------------|

| COMPARISON TO STATE OF THE | $\Delta RT$ |

| Ref.      | BW [Hz] | ENOB [b] | Cons. $[\mu A]$  | Supply [V] | Techn. [nm]     | DR [dB] | S. FOM [dB] | Arch. | Area [mm <sup>2</sup> ] | PSR [dB] |

|-----------|---------|----------|------------------|------------|-----------------|---------|-------------|-------|-------------------------|----------|

| [18]      | 150     | 12.2ª    | 20.8             | 1          | 65 <sup>b</sup> | 99.3    | 167.8       | CT_SB | 0.225                   | N.D.     |

| [15]      | 256     | 16.2     | 8.6              | 1.2/1      | 180             | 99.9    | 174.6       | DT-MB | 0.59                    | N.D.     |

| This work | 250     | 14.8     | 25               | 1.2        | 90              | 95.6    | 164.8       | DT-SB | 0.39                    | 76       |

| [39]      | 256     | 11.7     | 9.5              | 1.4        | 180             | 83      | 155.8       | CT-SB | 0.51                    | N.D.     |

| [41]      | 120     | 10.5     | 0.5              | 1.5        | 350             | 75.0    | 160.0       | DT-SB | 0.35                    | 32       |

| [46]      | 150     | 15       | 800°             | 1.8        | 130             | 112.0   | 162.2       | DT-SB | 0.4 <sup>d</sup>        | N.D.     |

| [43]      | 250     | 12.7     | 12.8             | 1.8        | 180             | 90      | 153.1       | CT-SB | 0.088                   | 92       |

| [44]      | 45      | 14.7     | 23               | 2.6        | 350             | 98      | 156.8       | DT-MB | 0.7                     | N.D.     |

| [19]      | 11      | 10.2     | 28               | 3.3        | 180             | 104     | 154.7       | CT_MB | 0.475 <sup>e</sup>      | N.D      |

| [50]      | 400     | 19.6     | 280              | 5          | 600             | 122     | 166         | DT-SB | 2                       | N.D      |

| [47]      | 400     | 19       | 540 <sup>f</sup> | 5          | 2000            | 116.1   | 168.7       | DT-MB | 4                       | N.D.     |

| [48]      | 10      | 16.7     | 240              | 5          | 700             | 121     | 160.2       | CT-MB | N.D.                    | N.D.     |

| [45]      | 100     | 16.4     | 101              | 5          | 180             | 110.1   | 163.1       | DT-SB | 0.8                     | 80       |

| [40]      | 100     | 12.8     | 400              | 5          | 700             | 82      | 129         | CT-SB | 3.3                     | 120      |

- <sup>a</sup> At the conditions for maximum DR (i.e. maximum input gain).

- <sup>b</sup> With 2.5-V thick-oxide transistors option.

- <sup>c</sup> Including decimation filter.

- <sup>d</sup> Including anti-aliasing and decimation filter.

- e Including optical sensor.

Fig. 18. Comparison of single-loop and low-pass  $\Sigma\Delta$  modulators with input bandwidth lower than 1-kHz and resolution higher than 10-b. The modulator supply voltage is reported if lower than 1.6 V.

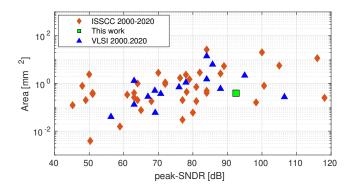

characterized over a large temperature range, with limited DR degradation at the highest temperature. The graph of Fig. 19 reports the silicon area vs peak-SNDR performance of the low-pass  $\Sigma\Delta$  modulators presented at the IEEE ISSCC and VLSI conferences in the 2000-2020 period. The proposed modulator is close to the state-of-the-art frontier thanks to the area minimization guaranteed by the low-noise opamp, which allows to reduce the value of the sampling capacitor. Moreover, the single-bit architecture does not require the additional circuit for DEM, which is mandatory with a multibit quantizer.

## VI. CONCLUSION

A third-order  $\Sigma\Delta$  modulator in 90-nm CMOS for the digitization of low-frequency signals was presented. A dedicated opamp was designed with local positive feedback and enhanced Miller compensation, through a common-gate stage, with fully-differential gain boosting. A mathematical model of

the opamp was presented, enabling a power-driven optimization of the amplifier and of the full modulator. Despite the low supply voltage, combined with a large input signal range, and the Miller compensation through a gain stage, the opamp exhibits low sensitivity to temperature and process variations. The modulator achieves the highest Figure of Merit among the state of the art  $\Sigma\Delta$  ADCs featuring more than 12.5-b effective resolution and a single sub-1.8-V supply. The silicon area is aligned with the state-of-the-art frontier. Furthermore, thanks to the proposed opamp architecture, the modulator exhibits the highest supply rejection compared to the low-voltage and small-bandwidth implementations in literature. The achieved performance makes the proposed modulator suitable for portable medical healthcare and diagnostic devices with multiple acquisition channels.

#### APPENDIX A

#### DETAILED CIRCUIT ANALYSIS OF THE LOW-NOISE OPAMP

The small-signal equivalent circuit of the left-side of the low-noise amplifier with improved Miller-Ahuja compensation

Fig. 19. Silicon area vs. peak-SNDR of SC- $\Sigma\Delta$  modulators published in the 2000-2020 period, from [53].

$$p_{1} \approx -\frac{1}{R_{out} C_{M} \cdot \left[1 + g_{m9} R_{C} \cdot \left(1 + \frac{g_{m13} g_{m17}}{g_{m9} g_{m15}}\right) + \frac{C_{out}}{C_{M} \cdot (1 + A_{aux-0})}\right]}$$

(27)

$$p_{2} \approx \frac{g_{m15} \cdot \left[ (1 + A_{aux-0}) \cdot \left( 1 + g_{m9} R_{C} + R_{C} \frac{g_{m13} g_{m17}}{g_{m15}} \right) + \frac{C_{out}}{C_{M}} \right]}{C_{D} \cdot \left[ (1 + A_{aux-0}) \cdot (1 + g_{m9} R_{C}) + \frac{C_{out}}{C_{M}} \right]}$$

(28)

$$|p_3| \approx \sqrt{\frac{g_{m9} g_{m19} \cdot (1 + A_{aux-0})}{C_C C_{out}}}$$

(29)

$$\delta_{3} \approx |p_{3}| \cdot \frac{\omega_{aux} \cdot \left[ R_{C} C_{C} \cdot (1 + A_{aux-0}) \cdot \left( 1 + \frac{C_{out}}{C_{M}} \right) + \frac{C_{out}}{g_{m19}} \cdot \left( 1 + g_{m15} R_{C} \frac{C_{C}}{C_{D}} \right) \right] + g_{m9} R_{C}}{2 \cdot \omega_{aux} \cdot (1 + A_{aux-0}) \cdot (1 + g_{m9} R_{C})}$$

(30)

$$z_{2} \approx \frac{g_{m19}r_{ds19} \cdot \left[R_{C}C_{D}g_{m9} \cdot (1 + A_{aux-0}) - C_{M}\frac{g_{m15}}{g_{m19}}\right]}{C_{M} \cdot \left[C_{D} \cdot (R_{C} + r_{ds19}) + C_{C}R_{C}g_{m15}r_{ds19}\right] - \frac{C_{D}R_{C}g_{m9}g_{m19}r_{ds19}}{\omega_{aux}}}$$

(31)

is shown in Fig. 4. Only the equivalent capacitance to ground has been considered for nodes C, D, E, whereas the effect of the drain-source resistance of MP3 has been neglected. The approximated equations of each equivalent capacitance and resistance in the circuit are:

$$R_C \approx \frac{1}{g_{m5} - g_{m7}}$$

(32)

$C_C \approx C_{gs5} + C_{gs6} + C_{gs9} + C_{gs12}$  (33)

$$C_C \approx C_{as5} + C_{as6} + C_{as9} + C_{as12}$$

(33)

$$C_D \approx C_{as15} + C_{as17} = C_{as15} \cdot (1 + k_{AB2})$$

(34)

$$R_{out} \approx r_{ds9} \parallel r_{ds11} \parallel r_{ds17} \tag{35}$$

$$C_{out} \approx C_L'$$

(36)

where  $r_{ds < i>}$  is the drain-source resistance of the i-th device,  $k_{AB2}$  is the current gain of MP15-MP17 mirror, i.e.  $k_{AB2} \equiv (W/L)_{MP17} / (W/L)_{MP15}$ , and  $C'_L$  is the effective load capacitance of the opamp in the integrator of Fig. 3, corresponding to the series of the feedback and sampling capacitor (i.e.  $C_{F-1}$  and  $C_{S-1}$ ) combined with the input capacitance of the adder and the SC-CMFB circuit.

Under the assumption of well-separated poles, the angular frequency of each pole is approximated with the coefficients of the denominator of the fifth-order transfer function in (10).

$$p_1 = -1/b_1 (37)$$

$$p_2 \approx -b_1/b_2 \tag{38}$$

$$|p_3| \approx \sqrt{b_2/b_4} \tag{39}$$

$$|p_{3}| \approx \sqrt{b_{2}/b_{4}}$$

$$\delta_{3} \equiv \frac{-\Re(p_{3})}{|p_{3}|} \approx \frac{p_{1}p_{2}|p_{3}|b_{3}}{2}$$

(39)

From these equations, approximate expressions are obtained for  $p_1$ ,  $p_2$ ,  $|p_3|$ , and  $\delta_3$ , as reported in (27), (28), (29), and (30), under the following assumptions:

$$g_{m19} r_{ds19} >> 1$$

(41)

$$g_{m9} R_{out} >> 1 \tag{42}$$

$$g_{m19} r_{ds19} > g_{m9} R_{out}$$

(43)

$$g_{m13} \approx g_{m15} \quad << \quad g_{m9} \tag{44}$$

$$g_{m13} \approx g_{m15} << g_{m19}$$

(45)

$$C_{out} > C_M$$

(46)

$$C_M \gg C_C, C_D$$

(47)

$$C_{M} >> C_{C}, C_{D}$$

$$\omega_{aux} >> \frac{g_{m3}}{C_{M}}$$

$$(48)$$

The value of  $C_{C-crit}$  is estimated by solving the following equation:

$$\delta_3(C_C = C_{C-crit}) = 1 \tag{49}$$

Under the assumption of  $z_1 << z_2 << |z_3|$ , a similar approximation as in (38) can be used for  $z_2$ , i.e.  $z_2 \approx -a_1/a_2$ , leading to (31).

The analytic expression of the unity-gain angular frequency of the integrator is obtained from (27) and considering that  $g_{m9} R_C >> 1$ , due to the local feedback in the first amplifier stage:

$$\omega_t = \beta A_{d-0} |p_1| \approx \beta \cdot \frac{g_{m3}}{C_M} \tag{50}$$

where  $\beta \equiv C_{F-1}/(C_{S-1}+C_{F-1})$  is the feedback factor in the integration phase.

#### REFERENCES

- [1] D. Remick, S. Kunkel, E. Holbrook, and C. Hanson, "Theory and applications of the polymerase chain reaction," American Journal of Clinical Pathology, vol. 93, no. 4 SUPPL. 1, pp. S49-S54, 1990.

- [2] F. Li and Others, "Quantitative and Rapid DNA Detection by Laser Transmission Spectroscopy," PLOS ONE, vol. 6, no. 12, pp. 1-6, 12

- [3] A. A. Aristov, E. V. Nosova, and A. N. Soldatov, "Use of Lying Drop Photometry for Clinical Laboratory Diagnostics," Biomedical Engineering, vol. 50, no. 5, pp. 314-317, Jan 2017.

- V. Bianchi, M. Mattarozzi, M. Giannetto, A. Boni, I. De Munari, and M. Careri, "A Self-Calibrating IoT Portable Electrochemical Immunosensor for Serum Human Epididymis Protein 4 as a Tumor Biomarker for Ovarian Cancer," Sensors, vol. 20, no. 7, 2020.

- [5] V. Bianchi, A. Boni, S. Fortunati, M. Giannetto, M. Careri, and I. De Munari, "A Wi-Fi Cloud-Based Portable Potentiostat for Electrochemical Biosensors," *IEEE Transactions on Instrumentation and Measurement*, vol. 69, no. 6, pp. 3232–3240, 2020.

- [6] D. Kilani, B. Mohammad, M. Alhawari, H. Saleh, and M. Ismail, "A Dual-Output Switched Capacitor DC-DC Buck Converter Using Adaptive Time Multiplexing Technique in 65-nm CMOS," *IEEE Transactions* on Circuits and Systems I: Regular Papers, vol. 65, no. 11, pp. 4007– 4016, 2018.

- [7] Z. Hua and H. Lee, "A Reconfigurable Dual-Output Switched-Capacitor DC-DC Regulator With Sub-Harmonic Adaptive-On-Time Control for Low-Power Applications," *IEEE Journal of Solid-State Circuits*, vol. 50, no. 3, pp. 724–736, 2015.

- [8] Q. Guo, J. Zhou, Q. Feng, R. Lin, H. Gong, Q. Luo, S. Zeng, M. Luo, and L. Fu, "Multi-channel fiber photometry for population neuronal activity recording," *Biomed. Opt. Express*, vol. 6, no. 10, pp. 3919–3931, Oct 2015

- [9] C. K. Kim, S. J. Yang, N. Pichamoorthy, N. P. Young, I. Kauvar, J. H. Jennings, T. N. Lerner, A. Berndt, S. Y. Lee, C. Ramakrishnan, T. J. Davidson, M. Inoue, H. Bito, and K. Deisseroth, "Simultaneous fast measurement of circuit dynamics at multiple sites across the mammalian brain," *Nature Methods*, vol. 13, no. 4, pp. 325–328, Apr 2016.

- [10] T. Akam and M. E. Walton, "pyphotometry: Open source python based hardware and software for fiber photometry data acquisition," *Scientific Reports*, vol. 9, no. 1, p. 3521, Mar 2019.

- [11] M. R. Kreifels, S. E. Whitney, and J. R. Termaat, "Real-time optical system for polymerase chain reaction," U.S. Patent US9 932 632B2, 2018.

- [12] (2021) Life Sciences & Medical Intrumentation.

Analog Devices, Inc. [Online]. Available: https://www.analog.com/en/applications/markets/healthcare-pavilion-home/life-sciences-medical-instrumentation/in-vitro-diagnostics.html

- [13] R. Schreier and G. Temes, Understanding Delta-Sigma Data Converters. Wiley-IEEE Press, 2005.

- [14] J. M. de la Rosa, R. Schreier, K. P. Pun, and S. Pavan, "Next-generation delta-sigma converters: Trends and perspectives," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 5, no. 4, pp. 484–499, Dec 2015.

- [15] S. Porrazzo, V. N. Manyam, A. Morgado, D. S. S. Bello, C. V. Hoof, A. H. M. van Roermund, R. F. Yazicioglu, and E. Cantatore, "A 1-V 99-to-75dB SNDR, 256Hz-16kHz bandwidth, 8.6-to-39μW reconfigurable SC ΣΔ Modulator for autonomous biomedical applications," in 2013 Proceedings of the ESSCIRC (ESSCIRC), Sept 2013, pp. 367–370.

- [16] R. T. Baird and T. S. Fiez, "Linearity enhancement of multibit delta; sigma; a/d and d/a converters using data weighted averaging," *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, vol. 42, no. 12, pp. 753–762, Dec 1995.

- [17] J. Yu and F. Maloberti, "A low-power multi-bit sigma; delta; modulator in 90-nm digital cmos without dem," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 12, pp. 2428–2436, Dec 2005.

- [18] J. Liang, S.-W. Sin, U. Seng-Pan, F. Maloberti, R. Martins, and H. Jiang, "A High DR High-Input-Impedance Programmable-Gain ECG Acquisition Interface with Non-inverting Continuous Time Sigma-Delta Modulator," in 2019 IEEE Asian Solid-State Circuits Conference (A-SSCC), 2019, pp. 309–312.

- [19] M. Noormohammadi Khiarak, S. Martel, Y. De Koninck, and B. Gosselin, "High-DR CMOS Fluorescence Biosensor With Extended Counting ADC and Noise Cancellation," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 66, no. 6, pp. 2077–2087, 2019.

- [20] L. Giuffredi, A. Boni, and M. Ronchi, "Low Power Low noise fully differential OpAmp," U.S. Patent 82 515 028, 2016.

- [21] R. Schreier. (2020, February) Delta sigma toolbox. Math-Works. [Online]. Available: https://www.mathworks.com/matlabcentral/ fileexchange/19-delta-sigma-toolbox

- [22] C. Enz and G. Temes, "Circuit techniques for reducing the effects of op-amp imperfections: autozeroing, correlated double sampling, and chopper stabilization," *Proceedings of the IEEE*, vol. 84, no. 11, pp. 1584–1614, Nov 1996.

- [23] K. Nagaraj, T. Viswanathan, K. Singhal, and J. Vlach, "Switched-capacitor circuits with reduced sensitivity to amplifier gain," *IEEE Transactions on Circuits and Systems*, vol. 34, no. 5, pp. 571–574, May 1987.

- [24] P. Malcovati, S. Brigati, F. Francesconi, F. Maloberti, P. Cusinato, and A. Baschirotto, "Behavioral modeling of switched-capacitor sigma-delta modulators," *IEEE Trans. Circuits Syst. I*, vol. 50, no. 3, pp. 352–364, Mar 2003.

- [25] F. Medeiro, A. Pérez-Verdú, B. Rez-Verd, and A. Rodríguez-Vázquez, Top-Down Design of High-Performance Sigma-Delta Modulators, ser. Kluwer international series in engineering and computer science: Analog circuits and signal processing. Springer, 1999.

- [26] J. Ruiz-Amaya, J. M. de la Rosa, F. V. Fernandez, F. Medeiro, R. del Rio, B. Perez-Verdu, and A. Rodriguez-Vazquez, "High-level synthesis of switched-capacitor, switched-current and continuous-time sigma; delta; modulators using simulink-based time-domain behavioral models," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 52, no. 9, pp. 1795–1810, Sept 2005.

- [27] A. Boni, L. Giuffredi, G. Pietrini, A. Magnanini, and M. Tonelli, "Design-oriented model for power-driven design optimization of SC-ΣΔ modulators," *International Journal of Circuit Theory and Applications*, vol. 46, no. 4, pp. 707–728, 2018.

- [28] R. Schreier, J. Silva, J. Steensgaard, and G. Temes, "Design-oriented estimation of thermal noise in switched-capacitor circuits," *IEEE Trans. Circuits Syst. I*, vol. 52, no. 11, pp. 2358–2368, Nov 2005.

- [29] S. Im and S.-G. Park, "Thermal noise analysis of switched-capacitor integrators with correlated double sampling," *International Journal of Circuit Theory and Applications*, vol. 44, no. 12, pp. 2101–2113, 2016, cTA-15-0244.R1.

- [30] F. Medeiro, B. Perez-Verdu, A. Rodriguez-Vazquez, and J. L. Huertas, "A vertically integrated tool for automated design of sigma; delta; modulators," *IEEE Journal of Solid-State Circuits*, vol. 30, no. 7, pp. 762–772, Jul 1995.

- [31] J. Roh, S. Byun, Y. Choi, H. Roh, Y.-G. Kim, and J.-K. Kwon, "A 0.9-V 60- μW 1-Bit Fourth-Order Delta-Sigma Modulator With 83-dB Dynamic Range," *IEEE J. Solid-State Circuits*, vol. 43, no. 2, pp. 361– 370. Feb 2008.

- [32] B. Ahuja, "An improved frequency compensation technique for cmos operational amplifiers," *Solid-State Circuits, IEEE Journal of*, vol. 18, no. 6, pp. 629–633, Dec 1983.

- [33] U. Dasgupta, "Issues in "Ahuja" Frequency Compensation Technique," in Radio-Frequency Integration Technology, 2009. RFIT 2009. IEEE International Symposium on, Jan 2009, pp. 326–329.

- [34] P. R. Gray and R. G. Meyer, "MOS operational amplifier design-A tutorial overview," *IEEE J. Solid-State Circuits*, vol. 17, no. 6, pp. 969– 982, Dec 1982.

- [35] D. Stefanovic and M. Kayal, Structured Analog CMOS Design. Springer, 2008.

- [36] M. Dessouky and A. Kaiser, "Very low-voltage digital-audio ΣΔ modulator with 88-dB dynamic range using local switch bootstrapping," Solid-State Circuits, IEEE Journal of, vol. 36, no. 3, pp. 349–355, Mar 2001.

- [37] A. Gerosa, A. Maniero, and A. Neviani, "A fully-integrated two-channel A/D interface for the acquisition of cardiac signals in implantable pacemakers," in ESSCIRC 2004 - 29th European Solid-State Circuits Conference (IEEE Cat. No.03EX705), 2003, pp. 157–160.

- [38] I. Lee, B. Kim, and B. G. Lee, "A Low-Power Incremental Delta-Sigma ADC for CMOS Image Sensors," *IEEE Trans. Circuits Syst. II*, vol. 63, no. 4, pp. 371–375, April 2016.

- [39] F. Cannillo, E. Prefasi, L. Hernández, E. Pun, F. Yazicioglu, and C. V. Hoof, "1.4V 13 μW 83dB DR CT-ΣΔ modulator with Dual-Slope quantizer and PWM DAC for biopotential signal acquisition," in 2011 Proceedings of the ESSCIRC (ESSCIRC), Sept 2011, pp. 267–270.

- [40] N. Sarhangnejad, R. Wu, Y. Chae, and K. A. A. Makinwa, "A continuous-time ΣΔ modulator with a Gm-C input stage, 120-dB CMRR and -87 dB THD," in *IEEE Asian Solid-State Circuits Conference* 2011, Nov 2011, pp. 245–248.

- [41] Y. Chae and G. Han, "Low Voltage, Low Power, Inverter-Based Switched-Capacitor Delta-Sigma Modulator," *IEEE J. Solid-State Cir*cuits, vol. 44, no. 2, pp. 458–472, Feb 2009.

- [42] K. Souri and K. A. A. Makinwa, "A 0.12 mm $^2$  7.4  $\mu$  W Micropower Temperature Sensor With an Inaccuracy of  $\pm 0.2$  °C (3  $\sigma$ ) From -30 °C to 125 °C," *IEEE Journal of Solid-State Circuits*, vol. 46, no. 7, 2011

- [43] A. Nikas, S. Jambunathan, L. Klein, M. Voelker, and M. Ortmanns, "A Continuous-Time Delta-Sigma Modulator Using a Modified Instrumentation Amplifier and Current Reuse DAC for Neural Recording," *IEEE Journal of Solid-State Circuits*, vol. 54, no. 10, pp. 2879–2891, 2019.

- [44] J. Johansson, H. Neubauer, and H. Hauer, "A 16-bit  $60\mu$ W Multi-Bit  $\Sigma\Delta$  modulator for portable ECG applications," in *ESSCIRC 2004 29th European Solid-State Circuits Conference*, Sept 2003, pp. 161–164.

- [45] L. Xu, B. Gönen, Q. Fan, J. H. Huijsing, and K. A. A. Makinwa, "A 110dB SNR ADC with  $\pm 30$ V input common-mode range and  $8\mu$ V Offset for current sensing applications," in 2015 IEEE International

- Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, Feb 2015, pp. 1–3.

- [46] C. Fraisse and A. Nagari, "A ΣΔ sense chain using chopped integrators for ultra-low-noise MEMS system," in ESSCIRC Conference 2016: 42nd European Solid-State Circuits Conference, Sept 2016, pp. 153–156.

- [47] O. Nys and R. K. Henderson, "A 19-bit low-power multibit sigma-delta ADC based on data weighted averaging," *IEEE J. Solid-State Circuits*, vol. 32, no. 7, pp. 933–942, Jul 1997.

- [48] G. Singh, R. Wu, Y. Chae, and K. A. A. Makinwa, "A 20bit continuous-time  $\Sigma\Delta$  modulator with a Gm-C integrator, 120dB CMRR and 15 ppm INL," in 2012 Proceedings of the ESSCIRC (ESSCIRC), Sept 2012, pp. 385–388.

- [49] D. A. Kerth, D. B. Kasha, T. G. Mellissinos, D. S. Piasecki, and E. J. Swanson, "A 126 dB linear switched-capacitor delta-sigma modulator," in *Solid-State Circuits Conference*, 1994. Digest of Technical Papers. 41st ISSCC., 1994 IEEE International, Feb 1994, pp. 196–197.

- [50] D. B. Kasha, W. L. Lee, and A. Thomsen, "A 16-mW, 120-dB linear switched-capacitor delta-sigma modulator with dynamic biasing," *IEEE J. Solid-State Circuits*, vol. 34, no. 7, pp. 921–926, Jul 1999.

- [51] M. N. Khiarak, E. Martianova, C. Bories, S. Martel, C. D. Proulx, Y. De Koninck, and B. Gosselin, "A Wireless Fiber Photometry System Based on a High-Precision CMOS Biosensor With Embedded Continuous-Time ΣΔ Modulation," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 12, no. 3, pp. 495–509, 2018.

- [52] J. de la Rosa. (2020) CMOS Sigma-Delta Modulators: State-of-the-Art Survey (December 2020). [Online]. Available: http://www.imse-cnm. csic.es/~jrosa/CMOS-SDMs-Survey-IMSE-JMdelaRosa.xlsx

- [53] B. Murmann. (2020) ADC Performance Survey 1997-2020. [Online]. Available: https://web.stanford.edu/~murmann/adcsurvey.html

Andrea Boni (Member, IEEE) received the M.Sc. degree in electronic engineering and the Ph.D. degree in information technologies from the University of Parma, Italy, in 1993 and 1997, respectively. From 1999 to 2002, he was a Research Assistant with the Department of Information Engineering, University of Parma. Since 2002, he has been an Associate Professor of Electronics with the University of Parma, where he is currently responsible for the Analog IC Design group. He has authored more than 80 scientific papers and two patents. His research

interests include the design of A/D converters, integrated sensor nodes, RFID devices, and sensor interface circuits. He was a Co-Founder of Silis S.r.l., a University spin-off company involved in the design of high-performance analog and mixed signal integrated circuits. He has been in the Technical Committee of the IEEE Custom Integrated Circuits Conference.

Luca Giuffredi received the M.Sc in Electronic Engineering in 2011 and the Ph.D. degree from the University of Parma in 2015. Since 2016 he has been with Silis S.r.l. as senior analog designer. His research interests are mainly in the area of low-power analog-to-digital converters in deep-submicron CMOS technologies.

Giorgio Pietrini received the PhD in Information Technology in March 2019 from the University of Parma, Italy, where he also earned the B.Sc. and M.Sc. degrees. From May 2019 he joined, as Postdoc Fellow, the McMaster Automotive Resource Centre (MARC) of the McMaster University in Hamilton (ON), Canada. His main research interests include integrated circuit design, especially high performance analog-to-digital converters, and electrical machine design with special regard to permanent magnet synchronous motors for automotive traction

and aerospace applications.

Marco Ronchi received the degree in Electronic Engineering from Politecnico di Milano, Italy in 1999. He Joined STMicroelectronics in 1999 where he is currently responsible for the design of Analog Low-Power Circuits for SRA – System Research and Applications Group. His research interests are primarily on low-power RF Transceiver and their applications in new and emerging wireless communication systems. other areas of investigation are low -power A/D converters, calibration and signal conditioning circuits for battery operated IoT nodes.

design.

Michele Caselli (member, IEEE) received the M.Sc in Electronic Engineering (cum laude) and the Ph.D. in Information Technologies at the Department of Engineering and Architecture, from the University of Parma, Italy, in 2015 and 2019 respectively. In 2019 he joined the imec Machine Learning program as mixed-signal designer, working on machine learning accelerators with emerging memory devices. His research interests include also design and optimization of RF energy harvesting circuits, low power IC analog design, and mixed signal power management